## 1.5A, Radiation Hardened, Positive, High Voltage LDO

### ISL75052SEH

The ISL75052SEH is a radiation hardened, single output LDO specified for an output current of 1.5A. The device operates from an input voltage range of 4.0V to 13.2V and provides for output voltages of 0.6V to 12.7V. The output is adjustable based on a resistor divider setting. Dropout voltages as low as 75mV (at 0.5A) typical can be realized using the device. This allows the user to improve the system efficiency by lowering V<sub>IN</sub> to nearly V<sub>OUT</sub>.

The ENABLE feature allows the part to be placed into a low shutdown current mode of 165µA (typical). When enabled, the device operates with a low ground current of 11mA (typical). which provides for operation with low quiescent power consumption.

The device has superior transient response and is designed keeping single event effects in mind. This results in reduction of the magnitude of SET seen on the output. There is no need for additional protection diodes and filters.

A COMP pin is provided to enable the use of external compensation. This is achieved by connecting a resistor and capacitor from COMP to ground. The device is stable with tantalum capacitors as low as 47µF (KEMET T525 series) and provides excellent regulation all the way from no load to full load. The programmable soft-start allows one to program the inrush current by means of the decoupling capacitor used on the BYP pin. The OCP pin allows the short-circuit output current limit threshold to be programmed by means of a resistor from OCP pin to GND. The OCP setting range is from a 0.16A minimum to 3.2A maximum. The resistor sets the constant current threshold for the output under fault conditions. The thermal shutdown disables the output if the device temperature exceeds the specified value. It will subsequently enter an ON/OFF cycle until the fault is removed.

## **Applications**

- · LDO regulator for space power systems

- DSP, FPGA and µP core power supplies

- · Post regulation of SMPS and down-hole drilling

### **Features**

- DLA SMD 5962-13220

- Input supply range 4.0V to 13.2V.

- Output current up to 1.5A at T<sub>j</sub> = +150°C

- Best in class accuracy ±1.5%

- Over line, load and temperature

- · Ultra low dropout:

- 75mV dropout (typical) at 0.5A

- 225mV dropout (typical) at 1.5A

- Noise of 100μV<sub>RMS</sub> (typical) between 300Hz to 300kHz

- · SET mitigation with no added filtering/diodes

- Shutdown current of 165µA (typical)

- · Externally adjustable output voltage

- PSRR 65dB (typical) at 1kHz

- · ENable and PGood feature

- · Programmable soft-start/inrush current limiting

- · Adjustable overcurrent protection

- Over-temperature shutdown

- Stable with 47µF minimum tantalum capacitor

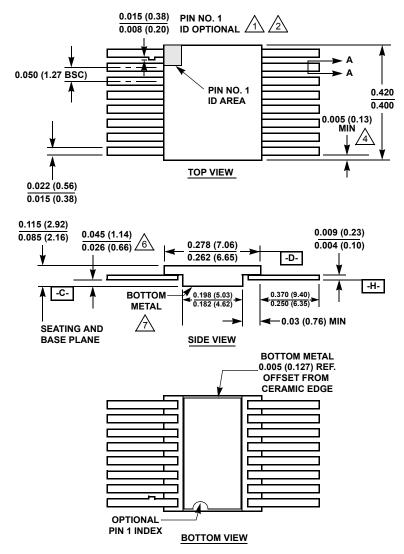

- Package 16 Ld flatpack

- Radiation environment

- High dose rate (50-300rad(Si)/s).....100krad(Si)

- Low dose rate (0.01rad(Si)/s)......100krad(Si)\*

- SET/SEL/SEB .......86MeV cm<sup>2</sup>/mg

## Related Literature

AN1850, "High Performance 3A LDO Evaluation Board User Guide"

AN1851, "Single-event Performance of the ISL75052SEH"

AN1852, "Radiation Report of the ISL75052SEH"

AN1878, "ISL75052SEH PSPICE Macro-Model"

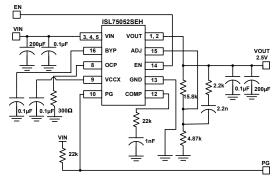

FIGURE 1. TYPICAL APPLICATION

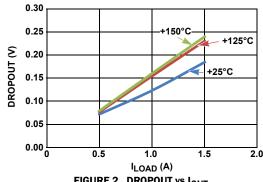

FIGURE 2. DROPOUT vs I<sub>OUT</sub>

<sup>\*</sup>Product capability established by initial characterization. The "EH" version is acceptance tested on a wafer-by-wafer basis to 50krad(Si) at low dose rate.

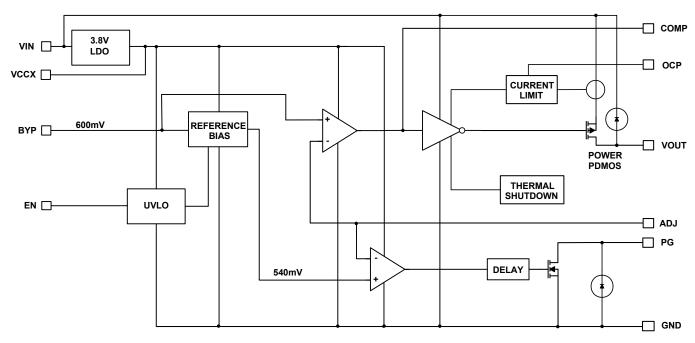

## **Block Diagram**

FIGURE 3. BLOCK DIAGRAM

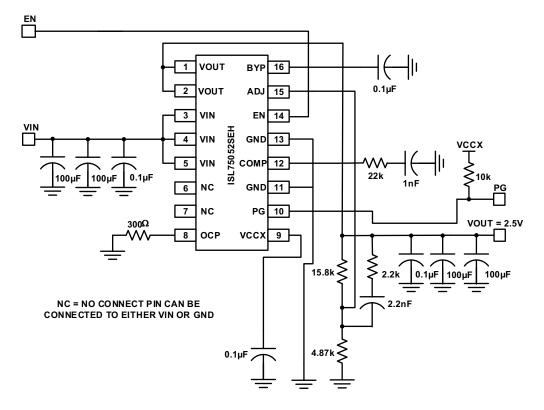

## **Typical Application**

**FIGURE 4. TYPICAL APPLICATION**

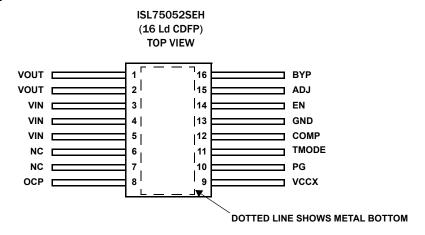

## **Pin Configuration**

## **Pin Descriptions**

| PIN NUMBER | PIN NAME               | DESCRIPTION                                                                                                                                              | ESD CIRCUIT |

|------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 3, 4, 5    | VIN                    | Input supply pins                                                                                                                                        | Circuit 1   |

| 10         | PG                     | This pin is logic high when $V_{\text{OUT}}$ is in regulation signal. A logic low defines when $V_{\text{OUT}}$ is not in regulation.                    | Circuit 2   |

| 13         | GND                    | GND pin. Pin 13 is also connected to the metal lid of the package.                                                                                       | Circuit 2   |

| 9          | vccx                   | The 3.8V internal bus is pinned out to accept a decoupling capacitor. Connect a 0.1µF ceramic capacitor from VCCX pin to GND.                            | Circuit 2   |

| 1, 2       | VOUT                   | Output voltage pins                                                                                                                                      | Circuit 1   |

| 12         | COMP                   | Add compensation capacitor and resistor between COMP and GND.                                                                                            | Circuit 2   |

| 15         | ADJ                    | ADJ pin allows V <sub>OUT</sub> to be programmed with an external resistor divider.                                                                      | Circuit 2   |

| 6, 7       | NC                     | No connect. May be grounded if needed.                                                                                                                   | Circuit 2   |

| 16         | ВҮР                    | Connect a 0.1µF capacitor from BYP pin to GND, to filter the internal VREF.                                                                              | Circuit 2   |

| 8          | OCP                    | OCP pin allows the current limit to be programmed with an external resistor.                                                                             | Circuit 2   |

| 14         | EN                     | V <sub>IN</sub> independent chip enable. TTL and CMOS compatible.                                                                                        | Circuit 2   |

| 11         | TMODE                  | Test Mode pin, must be connected to GND.                                                                                                                 | Circuit 2   |

|            | Bottom<br>Metalization | The metal surface on the bottom surface of the package is floating. For mounting instructions see <u>"Bottom Metal Mounting Guidelines" on page 15</u> . | Circuit 2   |

## **Ordering Information**

| ORDERING NUMBER (Note 2) | INTERNAL<br>MKT. NUMBER<br>(Note 1) | PART<br>MARKING        | TEMP RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG DWG. # |

|--------------------------|-------------------------------------|------------------------|-----------------|-----------------------------|------------|

| 5962R1322001VXC          | ISL75052SEHVFE                      | Q 5962R13 22001VXC     | -55 to +125     | 16 Ld CDFP                  | K16.E      |

| 5962R1322001V9A          | ISL75052SEHVX                       |                        | -55 to +125     | Die                         |            |

| ISL75052SEHF/SAMPLE      | ISL75052SEHX/SAMPLE                 |                        | -55 to +125     | Die Sample                  |            |

| ISL75052SEHFE/PROTO      | ISL75052SEHFE/PROTO                 | ISL75052 SEHFE / PROTO | -55 to +125     | 16 Ld CDFP                  | K16.E      |

| ISL75052SEHEVAL1Z        | Evaluation Board                    | •                      |                 | •                           | •          |

#### NOTES:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed in this "Ordering Information" table must be used when ordering.

4 intersil Submit Document Feedback FN8456.5

#### **Absolute Maximum Ratings**

| VIN Relative to GND Without Ion Beam (Note 3)           | 0.3 to +16.0V  |

|---------------------------------------------------------|----------------|

| V <sub>IN</sub> Relative to GND Under Ion Beam (Note 3) | 0.3 to +14.7V  |

| V <sub>OUT</sub> Relative to GND (Note 3)               | 0.3 to +14.7V  |

| PG, EN, OCP/ADJ, COMP, REFIN,                           |                |

| REFOUT Relative to GND (Note 3)                         | 0.3 to +6.5VDC |

| ESD Rating                                              |                |

| Human Body Model (Tested per MIL-PRF-883 30             | 15.7) 2kV      |

| Machine Model (Tested per JESD22-A115-A)                | 200V           |

| Charged Device Model (Tested per JESD22-C101            | .D)            |

|                                                         |                |

#### Recommended Operating Conditions (Note 4)

| Ambient Temperature Range (TA)                  | 55°C to +125°C |

|-------------------------------------------------|----------------|

| Junction Temperature (T <sub>J</sub> ) (Note 3) | +150°C         |

| V <sub>IN</sub> Relative to GND                 | 4.0V to 13.2V  |

| V <sub>OUT</sub> Range (Note 9)                 |                |

| PG, EN, OCP/ADJ Relative to GND                 |                |

#### **Thermal Information**

| Thermal Resistance (Typical)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (° C/W) |

|---------------------------------|----------------------|-----------------------|

| 16 Ld CDFP Package (Notes 6, 7) | 26                   | 4.5                   |

| Storage Temperature Range       | 6!                   | 5°C to +150°C         |

| Junction Temperature $(T_J)$    |                      | +175°C                |

#### **Radiation Information**

**Maximum Total Dose**

| High Dose (Dose Rate = 50-300radSi/s)                  | 100krads (Si)                              |

|--------------------------------------------------------|--------------------------------------------|

| Low Dose (Dose Rate = 10mradSi/s) (Note 5)             | 100krads (Si)                              |

| SET (V <sub>OUT</sub> within ±5% During Events)        | 86MeV/mg/cm <sup>2</sup>                   |

| SEL/B (No Latch-Up/Burnout)                            | .86MeV/mg/cm <sup>2</sup>                  |

| The output capacitance used for SEE testing is 2x100µF | for C <sub>IN</sub> and C <sub>OUT</sub> , |

| 100nF for BYPASS.                                      |                                            |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3. Extended operation at these conditions may compromise reliability. Exceeding these limits will result in damage. Recommended operating conditions define limits where specifications are guaranteed.

- 4. Refer to "Bottom Metal Mounting Guidelines" on page 15.

- 5. Product capability established by initial characterization. The "EH" version is acceptance tested on a wafer-by-wafer basis to 50krad(Si) at low dose rate.

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See TechBrief TB379.

- 7. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 8. Electromigration specification defined as lifetime average junction temperature of +150 °C where max rated DC current = lifetime average current.

- 9. SET performance of ±5% applies to V<sub>OUT</sub> ≥ 2.5V. For V<sub>OUT</sub> <2.5V SEE testing will need to be performed to ensure system SET goals are met.

**Electrical Specifications** Unless otherwise noted,  $V_{IN} = V_{OUT} + 0.5V$ ,  $V_{OUT} = 4.0V$ ,  $C_{IN} = C_{OUT} = 2x100 μF 60 mΩ$ , KEMET type T541X107N025AH or equivalent,  $T_J = +25 \,^{\circ}$ C,  $I_L = 0A$ . Applications must follow thermal guidelines of the package to determine worst case junction temperature. Please refer to "Applications Information" on page 15 of the data sheet and Tech Brief TB379. Boldface limits apply across the operating temperature range, -55 °C to +125 °C. Pulse load techniques used by ATE to ensure  $T_J = T_A$  defines guaranteed limits.

| PARAMETER                  | SYMBOL           | TEST CONDITIONS                                                                                                                    | MIN<br>( <u>Note 10</u> ) | TYP | MAX<br>( <u>Note 10</u> ) | UNIT |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| DC CHARACTERISTICS         |                  |                                                                                                                                    |                           |     |                           |      |

| DC Output Voltage Accuracy | V <sub>OUT</sub> | V <sub>OUT</sub> Resistor adjust to: 2.5V and 5.0V                                                                                 |                           |     |                           |      |

|                            |                  | $V_{OUT} = 2.5V, 4.0V < V_{IN} < 5.0V; 0A < I_{LOAD} < 1.5A,$<br>$T_{J} = .55$ °C to +125°C                                        | -1.5                      | 0.2 | 1.5                       | %    |

|                            |                  | $V_{OUT}$ = 2.5V, 4.0V < $V_{IN}$ < 5.0V; 0A < $I_{LOAD}$ < 1.5A, $T_J$ = +25 °C, post radiation                                   | -2.0                      | 0.2 | 2.0                       | %    |

|                            |                  | $V_{OUT} = 5.0V$ , $5.5V < V_{IN} < 6.9V$ ; $0A < I_{LOAD} < 1.5A$ ,<br>$T_{J} = -55$ °C to $+125$ °C                              | -1.5                      | 0.2 | 1.5                       | %    |

|                            |                  | $V_{OUT} = 5.0V$ , $5.5V < V_{IN} < 6.9V$ , $0A < I_{LOAD} < 1.5A$ , $T_{J} = +25$ °C, post radiation                              | -2.0                      | 0.2 | 2.0                       | %    |

|                            |                  | V <sub>OUT</sub> Resistor adjust to: 10.0V                                                                                         |                           |     |                           |      |

|                            |                  | $V_{OUT} = 10.0V, 10.5V < V_{IN} < 13.2V, I_{LOAD} = 0A,$<br>$T_{J} = .55 ^{\circ}C$ to +125 $^{\circ}C$                           | -1.5                      | 0.2 | 1.5                       | %    |

|                            |                  | $V_{OUT} = 10.0V$ , $10.5V < V_{IN} < 13.2V$ , $I_{LOAD} = 0A$ , $T_{J} = +25$ °C, post radiation                                  | -2.0                      | 0.2 | 2.0                       | %    |

|                            |                  | $V_{OUT} = 10.0V$ , $V_{IN} = 10.5V$ , $I_{LOAD} = 1.5A$ ,<br>$V_{IN} = 13.2V$ , $I_{LOAD} = 1.0A$ , $T_{J} = .55$ °C to +125°C    | -1.5                      | 0.2 | 1.5                       | %    |

|                            |                  | $V_{OUT} = 10.0V$ , $V_{IN} = 10.5V$ ; $I_{LOAD} = 1.5A$ , $V_{IN} = 13.2V$ , $I_{LOAD} = 1.0A$ , $T_{J} = +25$ °C, post radiation | -2.0                      | 0.2 | 2.0                       | %    |

Submit Document Feedback 5 Intersil\* FN8456.5

November 5, 2015

**Electrical Specifications** Unless otherwise noted,  $V_{IN} = V_{OUT} + 0.5V$ ,  $V_{OUT} = 4.0V$ ,  $C_{IN} = C_{OUT} = 2x100 μF 60 mΩ$ , KEMET type T541X107N025AH or equivalent,  $T_J = +25 °C$ ,  $I_L = 0$ A. Applications must follow thermal guidelines of the package to determine worst case junction temperature. Please refer to "Applications Information" on page 15 of the data sheet and Tech Brief TB379. Boldface limits apply across the operating temperature range, -55°C to +125°C. Pulse load techniques used by ATE to ensure  $T_J = T_A$  defines guaranteed limits. (Continued)

| PARAMETER                                                   | SYMBOL             | TEST CONDITIONS                                                                                                              | MIN<br>( <u>Note 10</u> ) | TYP  | MAX<br>( <u>Note 10</u> ) | UNIT              |

|-------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|-------------------|

| VCCX Pin                                                    | V <sub>VCCX</sub>  | $T_J = -55$ °C to +125°C; 4V < $V_{IN}$ < 13.2V; $I_{LOAD}$ = 0A                                                             | 3.7                       | 3.9  | 4.1                       | ٧                 |

| ADJ Pin                                                     | V <sub>ADJ</sub>   | T <sub>J</sub> = -55°C to +125°C                                                                                             | 591                       | 600  | 609                       | m۷                |

| ADJ Pin                                                     | V <sub>ADJ</sub>   | T <sub>J</sub> = 25 °C, post radiation                                                                                       | 588                       | 600  | 612                       | m۷                |

| BYP Pin                                                     | V <sub>BYP</sub>   | 4.0V < V <sub>IN</sub> < 13.2V; I <sub>LOAD</sub> = 0A,<br>T <sub>J</sub> = -55°C to +125°C                                  | 588                       | 600  | 612                       | mV                |

| DC Input Line Regulation                                    |                    | 4.0V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 2.5V                                                                      |                           | 1    | 8                         | m۷                |

|                                                             |                    | 5.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 5.0V                                                                      |                           | 1    | 20                        | m۷                |

|                                                             |                    | 10.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 10.0V                                                                    |                           | 1    | 10                        | m۷                |

| DC Output Load Regulation                                   |                    | V <sub>OUT</sub> = 2.5V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 4.0V                                               |                           | 0.3  | 9.0                       | m۷                |

|                                                             |                    | V <sub>OUT</sub> = 5.0V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 5.5V                                               |                           | 1.3  | 18.0                      | m۷                |

|                                                             |                    | V <sub>OUT</sub> = 10.0V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 10.5V                                             |                           | 0.1  | 36.0                      | mV                |

| ADJ Input Current                                           |                    | V <sub>ADJ</sub> = 0.6V                                                                                                      |                           |      | 1                         | μΑ                |

| Ground Pin Current                                          | IQ                 | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 0A, 4.0V < V <sub>IN</sub> < 13.2V                                              |                           | 6    | 10                        | mA                |

|                                                             |                    | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 1.5A, 4.0V < V <sub>IN</sub> < 13.2V                                            |                           | 8    | 12                        | mA                |

|                                                             |                    | V <sub>OUT</sub> = 10.0V, I <sub>LOAD</sub> = 0A, 11.0V < V <sub>IN</sub> < 13.2V                                            |                           | 15   | 20                        | mA                |

|                                                             |                    | V <sub>OUT</sub> = 10.0V, I <sub>LOAD</sub> = 1.5A, 11.0V < V <sub>IN</sub> < 13.2V                                          |                           | 20   | 25                        | mA                |

| Ground Pin Current in Shutdown                              | I <sub>SHDNL</sub> | ENABLE pin = 0V, V <sub>IN</sub> = 4.0V                                                                                      |                           | 70   | 120                       | μΑ                |

| Ground Pin Current in Shutdown                              | I <sub>SHDNH</sub> | ENABLE pin = 0V, V <sub>IN</sub> = 13.2V                                                                                     |                           | 165  | 300                       | μΑ                |

| Dropout Voltage (Note 12)                                   | V <sub>DO</sub>    | I <sub>LOAD</sub> = 0.5A, V <sub>OUT</sub> = 3.6V and 12.7V                                                                  |                           | 75   | 160                       | mV                |

|                                                             |                    | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 3.6V and 12.7V                                                                  |                           | 150  | 300                       | mV                |

|                                                             |                    | I <sub>LOAD</sub> = 1.5A, V <sub>OUT</sub> = 3.6V and 12.7V                                                                  |                           | 225  | 400                       | mV                |

| Output Short-Circuit Current for<br>16 Ld CDFP              | ISCL               | V <sub>OUT</sub> SET = 4.0V, V <sub>OUT</sub> + 0.5V < V <sub>IN</sub> < 13.2V,<br>R <sub>SET</sub> = 3k, ( <u>Note 14</u> ) | 0.16                      | 0.24 | 0.32                      | Α                 |

| Output Short-Circuit Current for 16 Ld CDFP                 | ISCH               | $V_{OUT}$ SET = 4.0V, $V_{OUT}$ + 0.5V < $V_{IN}$ < 13.2V,<br>$R_{SET}$ = 300 $\Omega$ , (Note 14)                           | 1.6                       | 2.4  | 3.2                       | Α                 |

| Thermal Shutdown Temperature (Note 11)                      | TSD                | V <sub>OUT</sub> + 0.5V < V <sub>IN</sub> < 13.2V                                                                            | 154                       | 175  | 196                       | °C                |

| Thermal Shutdown Hysteresis<br>(Rising Threshold) (Note 11) | TSDn               | V <sub>OUT</sub> + 0.5V < V <sub>IN</sub> < 13.2V                                                                            |                           |      | 25                        | °C                |

| AC CHARACTERISTICS                                          |                    |                                                                                                                              |                           |      |                           |                   |

| Input Supply Ripple Rejection (Note 11)                     | PSRR               | V <sub>P-P</sub> = 300mV, f = 1kHz, I <sub>LOAD</sub> = 1.5A;<br>V <sub>IN</sub> = 4.9V, V <sub>OUT</sub> = 4.0V             | 55                        | 65   |                           | dB                |

| Input Supply Ripple Rejection (Note 11)                     | PSRR               | V <sub>P-P</sub> = 300mV, f = 120Hz, I <sub>LOAD</sub> = 5mA;<br>V <sub>IN</sub> = 4.9V, V <sub>OUT</sub> = 2.5V             | 60                        | 70   |                           | dB                |

| Input Supply Ripple Rejection (Note 11)                     | PSRR               | V <sub>P-P</sub> = 300mV, f = 100kHz, I <sub>LOAD</sub> = 1.5A;<br>V <sub>IN</sub> = 4.9V, V <sub>OUT</sub> = 4.0V           | 40                        | 50   |                           | dB                |

| Phase Margin ( <u>Note 11</u> )                             | PM                 | $V_{OUT}$ = 2.5V, 4.0V and 10V, $C_{OUT}$ = 2x100 $\mu$ F, $R_{COMP}$ = 22k, $C_{COMP}$ = 1nF                                | 50                        |      |                           | 0                 |

| Gain Margin ( <u>Note 11</u> )                              | GM                 | $V_{OUT}$ = 2.5V, 4.0V and 10V $C_{OUT}$ = 2x100 $\mu$ F, $R_{COMP}$ = 22k, $C_{COMP}$ = 1nF                                 | 10                        |      |                           | dB                |

| Output Noise Voltage (Note 11)                              |                    | $V_{IN}$ = 4.1V, $V_{OUT}$ = 2.5V, $I_{LOAD}$ = 10mA, BW = 100Hz < f < 100kHz, BYPASS to GND capacitor = 0.2 $\mu$ F         |                           | 100  |                           | μV <sub>RMS</sub> |

Submit Document Feedback 6 Intersil\* FN8456.5

November 5, 2015

**Electrical Specifications** Unless otherwise noted,  $V_{IN} = V_{OUT} + 0.5V$ ,  $V_{OUT} = 4.0V$ ,  $C_{IN} = C_{OUT} = 2x100 μF 60 mΩ$ , KEMET type T541X107N025AH or equivalent,  $T_J = +25 \,^{\circ}$ C,  $I_L = 0A$ . Applications must follow thermal guidelines of the package to determine worst case junction temperature. Please refer to "Applications Information" on page 15 of the data sheet and Tech Brief TB379. Boldface limits apply across the operating temperature range, -55 °C to +125 °C. Pulse load techniques used by ATE to ensure  $T_J = T_A$  defines guaranteed limits. (Continued)

| PARAMETER                                                               | SYMBOL | TEST CONDITIONS                                                                                           | MIN<br>(Note 10) | TYP  | MAX<br>(Note 10) | UNIT              |

|-------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------|------------------|------|------------------|-------------------|

| DEVICE START-UP CHARACTERIS                                             | TICS   |                                                                                                           | <del>!</del>     |      | +                |                   |

| Enable Pin Characteristics                                              |        |                                                                                                           |                  |      |                  |                   |

| Turn-On Threshold                                                       |        | 4.0V < V <sub>IN</sub> < 13.2V                                                                            | 0.5              | 0.8  | 1.2              | ٧                 |

| Enable Pin Leakage Current                                              |        | V <sub>IN</sub> = 13.2V, EN = 5.5V                                                                        |                  |      | 1                | μΑ                |

| Enable Pin Propagation Delay (EN step 1.2V to V <sub>OUT</sub> = 100mV) |        | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ , $C_{OUT} = 22\mu F$ , $C_{BYP} = 0.2\mu F$       |                  | 0.5  | 1.0              | ms                |

| Enable Pin Turn-On Delay<br>(EN step 1.2V to PGOOD)                     |        | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ ,<br>$C_{OUT} = 2x100\mu F$ , $C_{BYP} = 0.2\mu F$ |                  | 1.4  | 3.0              | ms                |

| Enable Pin Turn-On Delay<br>(EN step 1.2V to PGOOD)                     |        | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ ,<br>$C_{OUT} = 22\mu F$ , $C_{BYP} = 0.2\mu F$    |                  | 1.1  | 2.5              | ms                |

| Hysteresis (Falling Threshold)                                          |        | 4.0V < V <sub>IN</sub> < 13.2V                                                                            | 75               | 170  |                  | m۷                |

| PG Pin Characteristics                                                  |        |                                                                                                           | ·                |      |                  |                   |

| V <sub>OUT</sub> Error Flag Rising Threshold                            |        |                                                                                                           | 83               | 88   | 94               | %V <sub>OUT</sub> |

| V <sub>OUT</sub> Error Flag Falling Threshold                           |        |                                                                                                           | 80               | 86   | 91               | %V <sub>OUT</sub> |

| V <sub>OUT</sub> Error Flag Hysteresis                                  |        |                                                                                                           | 1.75             | 2.50 |                  | %V <sub>OUT</sub> |

| Error Flag Low Voltage                                                  |        | I <sub>SINK</sub> = 1mA                                                                                   |                  | 5    | 100              | m۷                |

| Error Flag Low Voltage                                                  |        | I <sub>SINK</sub> = 10mA                                                                                  |                  | 5    | 400              | m۷                |

| Error Flag Leakage Current                                              |        | V <sub>IN</sub> = 13.2V, PG = 5.5V                                                                        |                  |      | 1                | μΑ                |

#### NOTES:

- 10. Parameters with bold face MIN and/or MAX limits are 100% tested at -55  $^{\circ}$  C, +25  $^{\circ}$  C and +125  $^{\circ}$  C.

- 11. Limits established by characterization and are not production tested.

- 12. Dropout is defined by the difference in supply VIN and VOUT when the supply produces a 2% drop in VOUT from its nominal value.

- 13. Refer to thermal package guidelines in "Bottom Metal Mounting Guidelines" on page 15.

- 14. OCP recovery overshoot should be within  $\pm 4\%$  of the nominal  $V_{OUT}$  setpoint.

- 15. SET performance of  $<\pm5\%$  at LET = 86MeV cm2/mg has been evaluated at  $V_{OUT}$  = >2.5V with  $C_{IN}$  =  $C_{OUT}$  = 2x100 $\mu$ F 10V 60m $\Omega$  in parallel with 0.1 $\mu$ F CDR04 X7R capacitor. Capacitor on BYP = 0.1 $\mu$ F CDR04 X7R.

# **High Dose Rate Post Radiation Characteristics** $T_A = +25\,^{\circ}$ C, unless otherwise noted. This data is typical test data post radiation exposure at a rate of 50 to 300rad(Si)/s. This data is intended to show typical parameter shifts due to high dose rate radiation (Note 16). These are not limits nor are they guaranteed.

| ITEM# | DESCRIPTION                    | TEST CONDITIONS                                                                                 | 0k RAD  | 100k RAD | UNIT |

|-------|--------------------------------|-------------------------------------------------------------------------------------------------|---------|----------|------|

| 1     | Enable Pin Leakage Current     | V <sub>IN</sub> = 13.2V, EN = 0V                                                                | -0.0375 | -0.0409  | μΑ   |

| 2     | Enable Pin Leakage Current     | V <sub>IN</sub> = 13.2V, EN = 5.5V                                                              | -0.0006 | 0.0005   | μΑ   |

| 3     | ADJ Input Current              | VADJ = 0.6V                                                                                     | -0.0007 | -0.0010  | μΑ   |

| 4     | Ground Pin Current in Shutdown | ENABLE Pin = 0V, V <sub>IN</sub> = 4.0V                                                         | 68.0    | 67.5     | μΑ   |

| 5     | Ground Pin Current in Shutdown | ENABLE Pin = 0V, V <sub>IN</sub> = 13.2V                                                        | 162.7   | 163.1    | μΑ   |

| 6     | ADJ Pin                        | V <sub>IN</sub> = 4.0V                                                                          | 0.60178 | 0.60489  | ٧    |

| 7     | BYP Pin                        | V <sub>IN</sub> = 4.0V ; I <sub>LOAD</sub> = 0A                                                 | 0.60075 | 0.60041  | ٧    |

| 8     | VCCX Pin                       | V <sub>IN</sub> = 4.0V ; I <sub>LOAD</sub> = 0A                                                 | 3.89156 | 3.87454  | ٧    |

| 9     | ADJ Pin                        | V <sub>IN</sub> = 13.2V                                                                         | 0.60183 | 0.60495  | ٧    |

| 10    | BYP Pin                        | V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A                                                 | 0.60105 | 0.60069  | ٧    |

| 11    | VCCX Pin                       | V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A                                                 | 3.89260 | 3.87503  | ٧    |

| 12    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°C | 2.51591 | 2.52880  | ٧    |

| 13    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 1.5A, = +25°C              | 2.51606 | 2.52893  | ٧    |

Submit Document Feedback 7 intersil FN8456.5

November 5, 2015

**High Dose Rate Post Radiation Characteristics**  $T_A = +25$  °C, unless otherwise noted. This data is typical test data post radiation exposure at a rate of 50 to 300rad(Si)/s. This data is intended to show typical parameter shifts due to high dose rate radiation (Note 16). These are not limits nor are they guaranteed. (Continued)

| ITEM# | DESCRIPTION                                   | TEST CONDITIONS                                                                      | Ok RAD   | 100k RAD | UNIT |

|-------|-----------------------------------------------|--------------------------------------------------------------------------------------|----------|----------|------|

| 14    | DC Output Voltage Accuracy                    | $V_{OUT} = 2.5V$ , $V_{IN} = 5.0V$ ; $I_{LOAD} = 0A$ , = +25°C                       | 2.51601  | 2.52879  | V    |

| 15    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 5.0V; I <sub>LOAD</sub> = 1.5A, = +25°C   | 2.51613  | 2.52894  | V    |

| 16    | DC Input Line Regulation                      | 4.0V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 2.5V                              | 0.41881  | 0.43023  | m۷   |

| 17    | DC Output Load Regulation                     | V <sub>OUT</sub> = 2.5V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 4.0V       | 0.15429  | 0.13063  | m۷   |

| 18    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 5.5V; I <sub>LOAD</sub> = 0A, = +25°C     | 5.02291  | 5.04849  | V    |

| 19    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 5.5V; I <sub>LOAD</sub> = 1.5A, = +25°C   | 5.02425  | 5.04984  | V    |

| 20    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 6.9V; I <sub>LOAD</sub> = 0A, = +25°C     | 5.02298  | 5.04900  | V    |

| 21    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 6.9V; I <sub>LOAD</sub> = 1.5A, = +25°C   | 5.02425  | 5.05003  | V    |

| 22    | DC Input Line Regulation                      | 5.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 5.0V                              | 0.43559  | 0.71168  | m۷   |

| 23    | DC Output Load Regulation                     | V <sub>OUT</sub> = 5.0V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 5.5V       | 1.34488  | 1.34957  | m۷   |

| 24    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 10.5V; I <sub>LOAD</sub> = 0A, = +25°C   | 10.05084 | 10.10237 | V    |

| 25    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 10.5V; I <sub>LOAD</sub> = 1.5A, = +25°C | 10.04956 | 10.10146 | V    |

| 26    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A, = +25°C   | 10.05112 | 10.10158 | V    |

| 27    | DC Output Voltage Accuracy                    | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 1.5A, = +25°C | 10.05334 | 10.10470 | V    |

| 28    | DC Input Line Regulation                      | 10.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 10.0V                            | 0.28300  | -0.78996 | m۷   |

| 29    | DC Output Load Regulation                     | V <sub>OUT</sub> = 10.0V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 10.5V     | -1.28285 | -0.90861 | m۷   |

| 30    | Ground Pin Current                            | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 4.0V              | 5.4      | 5.3      | mA   |

| 31    | Ground Pin Current                            | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 4.0V            | 7.1      | 7.1      | mA   |

| 32    | Ground Pin Current                            | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 13.2V             | 5.6      | 5.6      | mA   |

| 33    | Ground Pin Current                            | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 13.2V           | 5.6      | 5.6      | mA   |

| 34    | Ground Pin Current                            | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 4.0V             | 13.5     | 13.4     | mA   |

| 35    | Ground Pin Current                            | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 4.0V           | 13.8     | 13.8     | mA   |

| 36    | Ground Pin Current                            | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 13.2V            | 11.7     | 11.7     | mA   |

| 37    | Ground Pin Current                            | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 13.2V          | 13.3     | 13.6     | mA   |

| 38    | Dropout Voltage                               | I <sub>LOAD</sub> = 0.5A, V <sub>OUT</sub> = 3.6V                                    | 63.79    | 65.87    | m۷   |

| 39    | Dropout Voltage                               | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 3.6V                                    | 130.74   | 134.93   | m۷   |

| 40    | Dropout Voltage                               | I <sub>LOAD</sub> = 1.5A, V <sub>OUT</sub> = 3.6V                                    | 200.22   | 205.87   | m۷   |

| 41    | Dropout Voltage                               | I <sub>LOAD</sub> = 0.5A, V <sub>OUT</sub> = 12.7V                                   | 67.06    | 69.05    | m۷   |

| 42    | Dropout Voltage                               | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 12.7V                                   | 133.59   | 137.09   | m۷   |

| 43    | Dropout Voltage                               | I <sub>LOAD</sub> = 1.5A, V <sub>OUT</sub> = 12.7V                                   | 202.13   | 207.74   | m۷   |

| 44    | Error Flag Leakage Current                    | V <sub>IN</sub> = 13.2V, PG = 5.5V                                                   | -0.0404  | -0.0108  | uA   |

| 45    | Error Flag Low Voltage                        | I <sub>SINK</sub> = 1mA                                                              | 2.74     | 2.69     | m۷   |

| 46    | Error Flag Low Voltage                        | I <sub>SINK</sub> = 10mA                                                             | 2.95     | 2.89     | mV   |

| 47    | V <sub>OUT</sub> Error Flag Rising Threshold  | V <sub>IN</sub> = 13.2V                                                              | 88.6     | 88.0     | %    |

| 48    | V <sub>OUT</sub> Error Flag Falling Threshold | V <sub>IN</sub> = 13.2V                                                              | 86.1     | 85.5     | %    |

| 49    | V <sub>OUT</sub> Error Flag Hysteresis        | V <sub>IN</sub> = 13.2V                                                              | 2.5      | 2.5      | %    |

| 50    | V <sub>OUT</sub> Error Flag Rising Threshold  | V <sub>IN</sub> = 4.0V                                                               | 88.5     | 87.9     | %    |

| 51    | V <sub>OUT</sub> Error Flag Falling Threshold | V <sub>IN</sub> = 4.0V                                                               | 86.0     | 85.4     | %    |

| 52    | V <sub>OUT</sub> Error Flag Hysteresis        | V <sub>IN</sub> = 4.0V                                                               | 2.5      | 2.5      | %    |

| 53    | Turn-On Threshold (Rising)                    | V <sub>IN</sub> = 4.0V                                                               | 0.930    | 0.928    | V    |

| 54    | Hysteresis                                    | V <sub>IN</sub> = 4.0V                                                               | 163.8    | 163.3    | m۷   |

**High Dose Rate Post Radiation Characteristics**  $T_A = +25\,^{\circ}$ C, unless otherwise noted. This data is typical test data post radiation exposure at a rate of 50 to 300rad(Si)/s. This data is intended to show typical parameter shifts due to high dose rate radiation (Note 16). These are not limits nor are they guaranteed. (Continued)

| ITEM# | DESCRIPTION                                                             | TEST CONDITIONS                                                                                     | 0k RAD | 100k RAD | UNIT |

|-------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------|----------|------|

| 55    | Turn-On Threshold (Rising)                                              | V <sub>IN</sub> = 13.2V                                                                             | 0.981  | 0.975    | V    |

| 56    | Hysteresis                                                              | V <sub>IN</sub> = 13.2V                                                                             | 188.6  | 186.6    | m۷   |

| 57    | Enable Pin Propagation Delay (EN step 1.2V to V <sub>OUT</sub> = 100mV) | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ , $C_{OUT} = 22\mu F$ , $C_{BYP} = 0.2\mu F$ | 483.9  | 489.4    | μs   |

| 58    | Enable Pin Turn-On Delay (EN step 1.2V to PGOOD)                        | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ , $C_{OUT} = 22\mu F$ , $C_{BYP} = 0.2\mu F$ | 1007.6 | 984.1    | μs   |

| 59    | Enable Pin Turn-On Delay (EN step 1.2V to PGOOD)                        | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ , $C_{OUT} = 2x100\mu F$ , CBYP = $0.2\mu F$ | 1312.8 | 1319.1   | μs   |

| 60    | Output Short-Circuit Current                                            | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 4.5V, R <sub>SET</sub> = 3k                              | 0.235  | 0.234    | Α    |

| 61    | Output Short-Circuit Current                                            | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 13.2V, R <sub>SET</sub> = 3k                             | 0.240  | 0.239    | Α    |

| 62    | Output Short-Circuit Current                                            | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 4.5V, R <sub>SET</sub> = 300                             | 2.524  | 2.526    | Α    |

| 63    | Output Short-Circuit Current                                            | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 13.2V, R <sub>SET</sub> = 300                            | 2.538  | 2.540    | Α    |

**Low Dose Rate Post Radiation Characteristics**  $T_A = +25 \,^{\circ}$ C, unless otherwise noted. This data is typical test data post radiation exposure at a rate of 10mrad(Si)/s. This data is intended to show typical parameter shifts due to low dose rate radiation (Note 16). These are not limits nor are they guaranteed.

| ITEM# | DESCRIPTION                    | TEST CONDITIONS                                                                                     | 0k RAD   | 50k RAD  | 100k RAD | UNIT |

|-------|--------------------------------|-----------------------------------------------------------------------------------------------------|----------|----------|----------|------|

| 1     | Enable Pin Leakage Current     | V <sub>IN</sub> = 13.2V, EN = 0V                                                                    | -0.0390  | -0.0298  | -0.0290  | μΑ   |

| 2     | Enable Pin Leakage Current     | V <sub>IN</sub> = 13.2V, EN = 5.5V                                                                  | -0.0010  | 0.0092   | 0.0092   | μΑ   |

| 3     | ADJ Input Current              | V <sub>ADJ</sub> = 0.6V                                                                             | -0.0115  | -0.0070  | -0.0048  | μΑ   |

| 4     | Ground Pin Current in Shutdown | ENABLE Pin = OV, V <sub>IN</sub> = 4.0V                                                             | 68.8     | 65.1     | 67.0     | μΑ   |

| 5     | Ground Pin Current in Shutdown | ENABLE Pin = 0V, V <sub>IN</sub> = 13.2V                                                            | 163.4    | 159.9    | 161.9    | μΑ   |

| 6     | ADJ Pin                        | V <sub>IN</sub> = 4.0V                                                                              | 0.60162  | 0.60174  | 0.60107  | ٧    |

| 7     | BYP Pin                        | V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 0A                                                      | 0.60019  | 0.60048  | 0.60008  | ٧    |

| 8     | VCCX Pin                       | V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 0A                                                      | 3.88673  | 3.88170  | 3.87101  | ٧    |

| 9     | ADJ Pin                        | V <sub>IN</sub> = 13.2V                                                                             | 0.60168  | 0.60179  | 0.60113  | ٧    |

| 10    | BYP Pin                        | V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A                                                     | 0.60049  | 0.60057  | 0.60019  | ٧    |

| 11    | VCCX Pin                       | V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A                                                     | 3.88770  | 3.88246  | 3.87156  | ٧    |

| 12    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°C     | 2.51577  | 2.51488  | 2.51212  | ٧    |

| 13    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 4.0V; I <sub>LOAD</sub> = 1.5A, T <sub>A</sub> = +25°C   | 2.51596  | 2.51508  | 2.51228  | ٧    |

| 14    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 5.0V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°C     | 2.51598  | 2.51504  | 2.51225  | ٧    |

| 15    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 5.0V; I <sub>LOAD</sub> = 1.5A, T <sub>A</sub> = +25°C   | 2.51611  | 2.51520  | 2.51240  | ٧    |

| 16    | DC Input Line Regulation       | 4.0V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 2.5V                                             | 0.51044  | 0.44539  | 0.45274  | m۷   |

| 17    | DC Output Load Regulation      | V <sub>OUT</sub> = 2.5V; OA < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 4.0V                      | 0.19541  | 0.20233  | 0.16799  | m۷   |

| 18    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 5.5V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°C     | 5.02321  | 5.02138  | 5.01589  | ٧    |

| 19    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 5.5V; I <sub>LOAD</sub> = 1.5A, T <sub>A</sub> = +25°C   | 5.02434  | 5.02257  | 5.01708  | ٧    |

| 20    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 5.0V, V <sub>IN</sub> = 6.9V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°      | 5.02324  | 5.02155  | 5.01604  | ٧    |

| 21    | DC Output Voltage Accuracy     | $V_{OUT} = 5.0V$ , $V_{IN} = 6.9V$ ; $I_{LOAD} = 1.5A$ , $T_A = +25$ °C                             | 5.02443  | 5.02267  | 5.01717  | ٧    |

| 22    | DC Input Line Regulation       | 5.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 5.0V                                             | 0.10020  | 0.16807  | 0.20305  | m۷   |

| 23    | DC Output Load Regulation      | V <sub>OUT</sub> = 5.0V; OA < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 5.5V                      | 1.13716  | 1.19041  | 1.19966  | m۷   |

| 24    | DC Output Voltage Accuracy     | $V_{OUT} = 10.0V, V_{IN} = 10.5V; I_{LOAD} = 0A, T_A = +25°C$                                       | 10.04951 | 10.04602 | 10.03510 | ٧    |

| 25    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 10.5V; I <sub>LOAD</sub> = 1.5A, T <sub>A</sub> = +25°C | 10.04930 | 10.04583 | 10.03490 | ٧    |

| 26    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 0A, T <sub>A</sub> = +25°C   | 10.05009 | 10.04631 | 10.03535 | ٧    |

| 27    | DC Output Voltage Accuracy     | V <sub>OUT</sub> = 10.0V, V <sub>IN</sub> = 13.2V; I <sub>LOAD</sub> = 1.5A, T <sub>A</sub> = +25°C | 10.05191 | 10.04823 | 10.03735 | ٧    |

Low Dose Rate Post Radiation Characteristics  $T_A = +25$ °C, unless otherwise noted. This data is typical test data post radiation exposure at a rate of 10mrad(Si)/s. This data is intended to show typical parameter shifts due to low dose rate radiation (Note 16). These are not limits nor are they guaranteed. (Continued)

| 28 |                                                                            | TEST CONDITIONS                                                                                          | 0k RAD   | 50k RAD  | 100k RAD | UNIT |

|----|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------|----------|----------|------|

| 1  | DC Input Line Regulation                                                   | 10.5V < V <sub>IN</sub> < 13.2V, V <sub>OUT</sub> = 10.0V                                                | 0.58653  | 0.29418  | 0.24165  | m۷   |

| 29 | DC Output Load Regulation                                                  | V <sub>OUT</sub> = 10.0V; 0A < I <sub>LOAD</sub> < 1.5A, V <sub>IN</sub> = 10.5V                         | -0.20163 | -0.18742 | -0.19485 | m۷   |

| 30 | Ground Pin Current                                                         | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 4.0V                                  | 5.5      | 5.8      | 6.3      | mA   |

| 31 | Ground Pin Current                                                         | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 4.0V                                | 7.2      | 7.4      | 8.0      | mA   |

| 32 | Ground Pin Current                                                         | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 13.2V                                 | 5.6      | 5.9      | 6.5      | mA   |

| 33 | Ground Pin Current                                                         | V <sub>OUT</sub> = 2.5V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 13.2V                               | 5.6      | 5.9      | 6.5      | mA   |

| 34 | Ground Pin Current                                                         | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 4.0V                                 | 14.0     | 14.3     | 14.9     | mA   |

| 35 | Ground Pin Current                                                         | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 4.0V                               | 14.1     | 14.5     | 15.0     | mA   |

| 36 | Ground Pin Current                                                         | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 0A, V <sub>IN</sub> = 13.2V                                | 11.9     | 12.3     | 12.8     | mA   |

| 37 | Ground Pin Current                                                         | V <sub>OUT</sub> = 10.0V; I <sub>LOAD</sub> = 1.5A, V <sub>IN</sub> = 13.2V                              | 13.5     | 13.9     | 14.3     | mA   |

| 38 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 0.5A, V <sub>OUT</sub> = 3.6V                                                        | 67.19    | 68.88    | 69.98    | m۷   |

| 39 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 3.6V                                                        | 138.01   | 140.62   | 142.81   | m۷   |

| 40 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 1.5A, V <sub>OUT</sub> = 3.6V                                                        | 210.09   | 213.41   | 216.95   | m۷   |

| 41 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 0.5A, V <sub>OUT</sub> = 12.7V                                                       | 70.54    | 72.94    | 73.03    | m۷   |

| 42 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 1.0A, V <sub>OUT</sub> = 12.7V                                                       | 140.61   | 143.23   | 145.05   | m۷   |

| 43 | Dropout Voltage                                                            | I <sub>LOAD</sub> = 1.5A, V <sub>OUT</sub> = 12.7V                                                       | 212.35   | 215.80   | 219.56   | m۷   |

| 44 | Error Flag Leakage Current                                                 | V <sub>IN</sub> = 13.2V, PG = 5.5V                                                                       | -0.0581  | -0.0364  | -0.0385  | uA   |

| 45 | Error Flag Low Voltage                                                     | I <sub>SINK</sub> = 1mA                                                                                  | 2.72     | 2.81     | 2.74     | m۷   |

| 46 | Error Flag Low Voltage                                                     | I <sub>SINK</sub> = 10mA                                                                                 | 2.92     | 2.97     | 2.94     | m۷   |

| 47 | V <sub>OUT</sub> Error Flag Rising Threshold                               | V <sub>IN</sub> = 13.2V                                                                                  | 88.6     | 88.5     | 88.5     | %    |

| 48 | V <sub>OUT</sub> Error Flag Falling Threshold                              | V <sub>IN</sub> = 13.2V                                                                                  | 86.0     | 86.0     | 86.0     | %    |

| 49 | V <sub>OUT</sub> Error Flag Hysteresis                                     | V <sub>IN</sub> = 13.2V                                                                                  | 2.5      | 2.5      | 2.5      | %    |

| 50 | V <sub>OUT</sub> Error Flag Rising Threshold                               | V <sub>IN</sub> = 4.0V                                                                                   | 88.4     | 88.4     | 88.4     | %    |

| 51 | V <sub>OUT</sub> Error Flag Falling Threshold                              | V <sub>IN</sub> = 4.0V                                                                                   | 85.9     | 85.9     | 85.9     | %    |

| 52 | V <sub>OUT</sub> Error Flag Hysteresis                                     | V <sub>IN</sub> = 4.0V                                                                                   | 2.5      | 2.5      | 2.5      | %    |

| 53 | Turn-On Threshold (Rising)                                                 | V <sub>IN</sub> = 4.0V                                                                                   | 0.925    | 0.923    | 0.918    | ٧    |

| 54 | Hysteresis                                                                 | V <sub>IN</sub> = 4.0V                                                                                   | 162.6    | 161.3    | 162.1    | m۷   |

| 55 | Turn-On Threshold (Rising)                                                 | V <sub>IN</sub> = 13.2V                                                                                  | 0.975    | 0.972    | 0.966    | ٧    |

| 56 | Hysteresis                                                                 | V <sub>IN</sub> = 13.2V                                                                                  | 186.9    | 185.0    | 185.4    | m۷   |

|    | Enable Pin Propagation Delay (EN step<br>1.2V to V <sub>OUT</sub> = 100mV) |                                                                                                          |          | 531.8    | 540.0    | μs   |

|    | Enable Pin Turn-On Delay (EN step 1.2V to PGOOD)                           | $V_{IN} = 4.5V$ , $V_{OUT} = 4.0V$ , $I_{LOAD} = 1.5A$ , $C_{OUT} = 22\mu F$ , $C_{BYP} = 0.2\mu F$      |          | 1031.8   | 1038.2   | μs   |

|    | Enable Pin Turn-On Delay (EN step 1.2V to PGOOD)                           | $V_{IN}$ = 4.5V, $V_{OUT}$ = 4.0V, $I_{LOAD}$ = 1.5A, $C_{OUT}$ = 2x100 $\mu$ F, $C_{BYP}$ = 0.2 $\mu$ F | 1297.9   | 1305.7   | 1317.4   | μs   |

| 60 | Output Short-Circuit Current                                               | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 4.5V, R <sub>SET</sub> = 3k                                   |          | 0.236    | 0.238    | Α    |

| 61 | Output Short-Circuit Current                                               | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 13.2V, R <sub>SET</sub> = 3k                                  |          | 0.241    | 0.242    | Α    |

| 62 | Output Short-Circuit Current                                               | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 4.5V, R <sub>SET</sub> = 300                                  | 2.575    | 2.564    | 2.568    | Α    |

| 63 | Output Short-Circuit Current                                               | V <sub>OUT</sub> = 4.0V, V <sub>IN</sub> = 13.2V, R <sub>SET</sub> = 300                                 | 2.584    | 2.573    | 2.579    | Α    |

NOTE:

16. See the Radiation report.

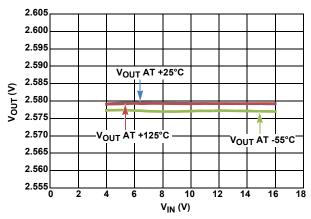

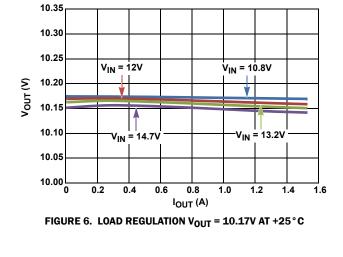

## **Typical Operating Performance**

FIGURE 5. LINE REGULATION vs TEMPERATURE (°C),  $V_{OUT}$  = 2.579V,  $I_{OUT}$  = 0mA

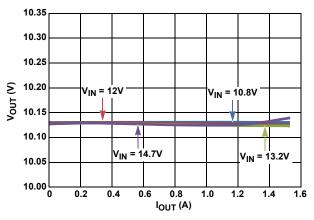

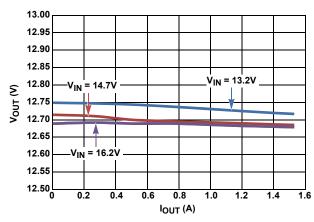

FIGURE 7. LOAD REGULATION VOUT = 10.13V AT +125°C

FIGURE 8. LOAD REGULATION V<sub>OUT</sub> = 10.22V AT -55°C

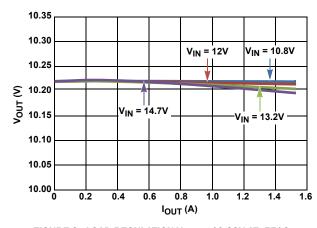

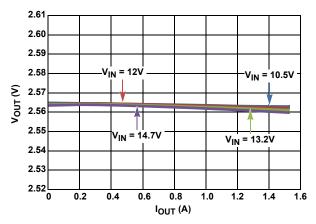

FIGURE 9. LOAD REGULATION V<sub>OUT</sub> = 2.567V AT +25°C

FIGURE 10. LOAD REGULATION  $\rm V_{OUT}$  = 2.571V AT +125  $^{\circ}$  C

## Typical Operating Performance (Continued)

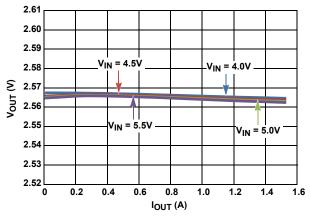

FIGURE 11. LOAD REGULATION  $V_{OUT}$  = 2.564V AT -55 °C

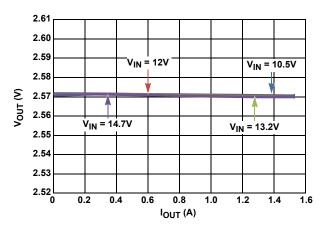

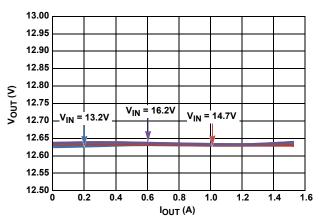

FIGURE 12. LOAD REGULATION  $V_{OUT} = 12.75V \text{ AT } +25^{\circ}\text{C}$

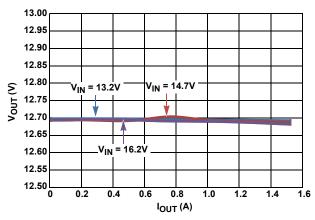

FIGURE 13. LOAD REGULATION V<sub>OUT</sub>= 12.63V AT +125°C

FIGURE 14. LOAD REGULATION V<sub>OUT</sub> = 12.7V AT -55 °C

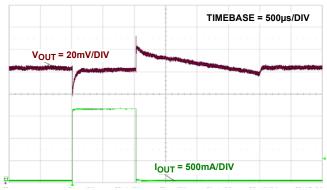

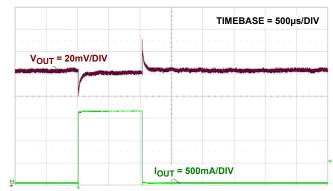

FIGURE 15. LOAD STEP RESPONSE +25 °C,  $V_{IN}$  = 4.0V,  $V_{OUT}$  = 2.5V,  $I_{OUT}$  = 0A TO 1.6A,  $C_{OUT}$  = 200µF,  $30m\Omega$ ,

FIGURE 16. LOAD STEP RESPONSE, +25 °C,  $V_{IN}$  = 4.0V,  $V_{OUT}$  = 2.5V,  $I_{OUT}$  = 0.15A TO 1.6A,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$

## Typical Operating Performance (Continued)

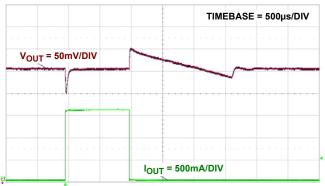

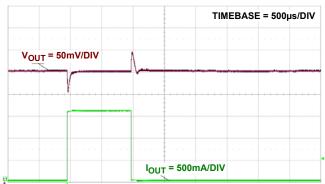

FIGURE 17. LOAD STEP RESPONSE, +25 °C,  $V_{IN}$  = 13.2V,  $V_{OUT}$  = 10V,  $I_{OUT}$  = 0A TO 1.5A,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$

FIGURE 18. LOAD STEP RESPONSE, +25 ° C,  $V_{IN}$  = 13.2V,  $V_{OUT}$  = 10V,  $I_{OUT}$  = 0.15A TO 1.5A,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$

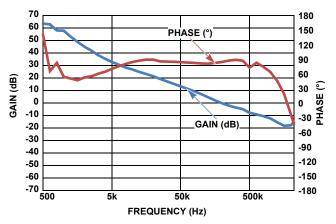

FIGURE 19. GAIN PHASE PLOTS,  $V_{IN}$  = 4V,  $V_{OUT}$  = 2.5V,  $I_{OUT}$  = 1.5A,  $R_{COMP}$  = 22k,  $C_{COMP}$  = 1nF,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$ , PHASE MARGIN = 98.68°, GAIN MARGIN = 23.01dB

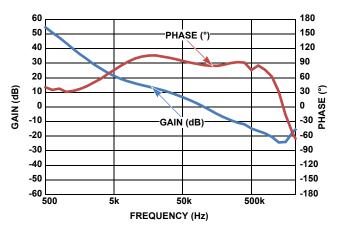

FIGURE 20. GAIN PHASE PLOTS,  $V_{IN}$  = 11V,  $V_{OUT}$  = 10V,  $I_{OUT}$  = 1.5A,  $R_{COMP}$  = 22k,  $C_{COMP}$  = 1nF,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$ , PHASE MARGIN = 84.56°, GAIN MARGIN = 18.06dB

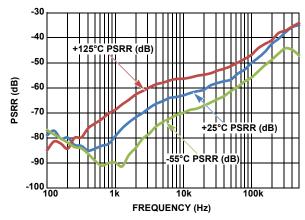

FIGURE 21. PSRR,  $V_{IN}$  = 4.9V,  $V_{OUT}$  = 4.0V,  $I_{OUT}$  = 1.5A,  $R_{COMP}$  = 22k,  $C_{COMP}$  = 1nF,  $C_{OUT}$  = 200 $\mu$ F, 30m $\Omega$

Submit Document Feedback 13 FN8456.5 November 5, 2015

## Typical Operating Performance (Continued)

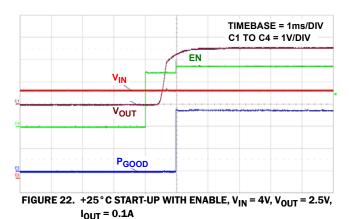

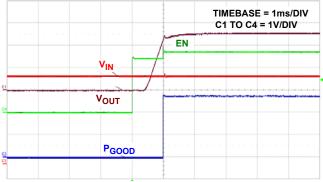

FIGURE 23. +25 °C START-UP WITH ENABLE,  $V_{IN}$  = 4V,  $V_{OUT}$  = 2.5V,  $I_{OUT}$  = 1.5A

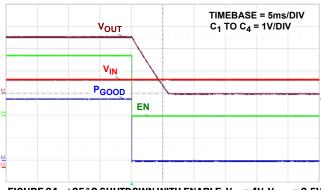

FIGURE 24. +25 °C SHUTDOWN WITH ENABLE,  $V_{\text{IN}}$  = 4V,  $V_{\text{OUT}}$  = 2.5V,  $I_{\text{OUT}}$  = 0.1A

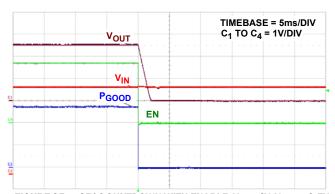

FIGURE 25. +25 ° C SHUTDOWN WITH ENABLE,  $V_{IN}$  = 4V,  $V_{OUT}$  = 2.5V,  $I_{OUT}$  = 1.5A

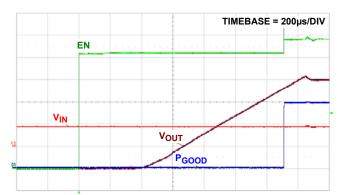

FIGURE 26. +25 °C PROPAGATION DELAY,  $V_{IN}$  = 4.5V,  $V_{OUT}$  = 4V,  $I_{OUT}$  = 1.5A, EN 50% TO  $V_{OUT}$  5%

## **Applications Information**

#### **Input Voltage Requirements**

This RH LDO will work from a  $V_{\mbox{\footnotesize{IN}}}$  in the range of 4.0V to 13.2V. The input supply can have a tolerance of as much as ±10% for conditions noted in the specification table. The minimum guaranteed input voltage is 4.0V. However, due to the nature of an LDO, VIN must be some margin higher than the output voltage plus dropout at the maximum rated current of the application if active filtering (PSRR) is expected from V<sub>IN</sub> to V<sub>OUT</sub>. The Dropout specification of this family of LDOs has been generously specified in order to allow design for efficient operation.

#### **External Capacitor Requirements**

#### **GENERAL GUIDELINE**

External capacitors are required for proper operation. Careful attention must be paid to layout guidelines and selection of capacitor type and value to ensure optimal performance.

#### **OUTPUT CAPACITOR**

It is recommended to use a combination of tantalum and ceramic capacitors to achieve a good volume to capacitance ratio. The recommended combination is a  $2x100\mu F 60m\Omega$  rated, KEMET T541 series tantalum capacitor, in parallel with a 0.1µF MIL-PRF-49470 ceramic capacitor to be connected to V<sub>OLIT</sub> and ground pins of the LDO with PCB traces no longer than 0.5cm.

#### INPUT CAPACITOR

It is recommended to use a combination of tantalum and ceramic capacitors to achieve a good capacitance to volume ratio. The recommended combination is a  $2x100\mu F 60m\Omega$  rated. KEMET T541 series tantalum capacitor in parallel with a 0.1µF MIL-PRF-49470 ceramic capacitor to be connected to V<sub>IN</sub> and ground pins of the LDO with PCB traces no longer than 0.5cm.

#### **Current Limit Protection**

The RH LDO incorporates protection against overcurrent due to any short or overload condition applied to the output pin. The current limit circuit performs as a constant current source when the output current exceeds the current limit threshold, which can be adjusted by means of a resistor connected between the OCP pin and GND. If the short or overload condition is removed from V<sub>OUT</sub>, then the output returns to normal voltage mode regulation. In the event of an overload condition, the LDO will begin to cycle on and off due to the die temperature exceeding thermal fault condition. However, one may never witness thermal cycling if the heatsink used for the package can keep the die temperature below the limits specified for thermal shutdown. The ROCP can be calculated using Equation 1:

$$\mathsf{R}_{\mathsf{OCP}} = \frac{762.8}{\mathsf{I}_{\mathsf{OCP}} - (1.382\mathsf{E-}03 \bullet \mathsf{V}_{\mathsf{IN}}) - (2.629\mathsf{E-}04 \bullet \mathsf{T}_{\mathsf{A}}) + 4.493\mathsf{E-}02}$$

(EQ. 1)

ROCP = The OCP setting resistor in ohms.

V<sub>IN</sub> = Supply voltage in volts.

$I_{OCP}$  = The required OCP threshold in amps.

$T_{\Delta}$  = The ambient temperature in °C.

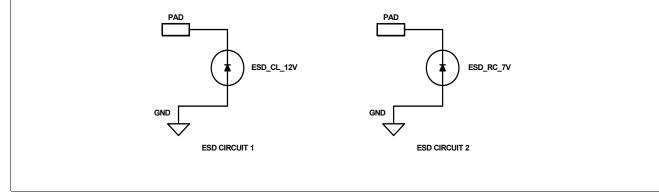

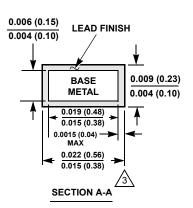

#### **ESD Clamps**

The ESD CL 12V ESD clamps break down at nominally 17V. The ESD\_RC\_7V clamps break down at nominally 7.5V with a tolerance of ±10%. The PG pin has a diode to GND. The VOUT pin has a diode to VIN (see "Pin Descriptions" on page 3).

#### **Soft-Start**

Soft-start is achieved by means of the charging time constant of the BYP pin. The capacitor value on the pin determines the time constant and can be calculated using Equation 2:

$$t_{SS} = (3.3338E-6 \times C_{BYP}) + (9.5725E-8 \times T_A) - 9.2628E-6$$

(EQ. 2)

#### Where

$t_{SS}$  = Soft-start time in seconds.

CBYP = Bypass capacitance in nF.

$T_A$  = Ambient temperature in °C.

#### **COMP Pin**

This pin helps compensate the device for various load conditions. For 4.0V < VIN < 6.0V use RCOMP = 40k and CCOMP = 1nF. For 6V < VIN < 13.2V use RCOMP = 40k and CCOMP = 4.7nF. The maximum current of the COMP pin when shorted to GND is 160µA.

#### **Undervoltage Lockout**

The undervoltage lockout function detects when VCCX exceeds 3.2V. When that level is reached, the LDO feedback loop is closed and the LDO can begin regulating. This is achieved by freeing the BYP net to charge up and act as a reference voltage to the EA. Prior to that happening, the LDO Power PMOS device is clamped

#### **Bottom Metal Electrical Potential**

The package bottom metal is electrically isolated and unbiased. The bottom metal may be electrically connected to any potential, which offers the best thermal path through conductive mounting materials (conductive epoxy, solder, etc.) or may be left unbiased through the use of electrically nonconductive mounting materials (nonconductive epoxy, Sil-pad, kapton film, etc.).

#### **Bottom Metal Mounting Guidelines**

The package bottom is a solderable metal surface. The following JESD51-5 guidelines may be used to mount the package:

- Place a thermal land on the PCB under the bottom metal.

- The land should be approximately the same size to 1mm larger than the 0.19inx0.41in bottom metal.

- · Place an array of thermal vias below the thermal land.

- Via array size: ~4 x 9 = 36 thermal vias

- Via diameter: ~0.3mm drill diameter with plated copper on the inside of each via.

- Via pitch: ~1.2mm.

Vias should drop to and contact as much buried metal area as feasible to provide the best thermal path.

#### **Thermal Fault Protection**

In the event the die temperature exceeds +170 °C (typical) the output of the LDO will shut down until the die temperature can cool down to +150 °C (typical). The level of power combined with the thermal impedance of the package ( $\theta_{JC}$  of 5 °C/W for the 16 Ld CDFP package) will determine if the junction temperature exceeds the thermal shutdown temperature specified in the specification table (see "Bottom Metal Mounting Guidelines" on page 15).

Submit Document Feedback 16 FN8456.5 November 5, 2015

## **Package Characteristics**

### **Weight of Packaged Device**

0.59 Grams (Typical)

#### **Lid Characteristics**

Finish: Gold

Potential: Connected to Pin 13 (GND)

Case Isolation to Any Lead: 20 x  $10^9 \Omega$  (minimum)

### **Die Characteristics**

#### **Die Dimensions**

2819µm x 5638µm (111mils x 222mils).

Thickness:  $304.8\mu m \pm 25.4\mu m (12.0 mils \pm 1 mil)$

#### **Interface Materials**

#### **GLASSIVATION**

Type: Silicon Oxide and Silicon Nitride

Thickness:  $0.3\mu m \pm 0.03\mu m$  to  $1.2\mu m \pm 0.12\mu m$

#### **TOP METALLIZATION**

Type: AlCu (99.5%/0.5%) Thickness:  $2.7\mu m \pm 0.4\mu m$

#### **SUSTRATE**

Type: Silicon

#### **BACKSIDE FINISH**

Silicon

#### **Assembly Related Information**

#### SUBSTRATE POTENTIAL

Ground

#### **Additional Information**

#### **WORST CASE CURRENT DENSITY**

$<2 \times 10^5 \text{ A/cm}^2$

#### **TRANSISTOR COUNT**

1074

#### **PROCESS**

0.6µm BiCMOS Junction Isolated

## **Metallization Mask Layout**

**TABLE 1. DIE LAYOUT X-Y COORDINATES**

| PAD | х    | Y    | DX  | DY  | PIN NAME |

|-----|------|------|-----|-----|----------|

| 1   | 1019 | 1021 | 185 | 450 | VOUT     |

| 2   | 1249 | 390  | 185 | 449 | VOUT     |

| 3   | 3070 | 1030 | 185 | 450 | VIN      |

| 4   | 3300 | 399  | 185 | 450 | VIN      |

| 5   | 5037 | 256  | 185 | 185 | OCP      |

| 6   | 5253 | 1635 | 185 | 185 | vcc      |

| 7   | 5099 | 2436 | 185 | 185 | PG       |

| 8   | 4635 | 2436 | 185 | 185 | NC       |

| 9   | 3824 | 2436 | 185 | 185 | COMP     |

| 10  | 2840 | 1660 | 185 | 450 | VIN      |

| 11  | 1799 | 2436 | 185 | 185 | GND      |

| 12  | 668  | 2436 | 185 | 185 | EN       |

| 13  | 168  | 2381 | 185 | 185 | ADJ      |

| 14  | 168  | 1972 | 185 | 184 | ВҮР      |

| 15  | 789  | 1652 | 185 | 450 | VOUT     |

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 5, 2015   | FN8456.5 | Updated Equation 1 on page 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| August 31, 2015    | FN8456.4 | Updated Equation 2 on page 15. Thermal Information table on page 5: Removed reference to TB493.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| December 4, 2014   | FN8456.3 | Updated Figure 1 for clarity.  Added ESD Ratings to "Absolute Maximum Ratings" on page 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| July 11, 2014      | FN8456.2 | <ol> <li>Pages 7 thru 10 - Added Radiation tables</li> <li>Page 15 - Added paragraph for Soft Start: "The Soft-start is achieved by means of the charging time constant of the BYP pin. The capacitor value on the pin determines the time constant and can be calculated using Equation 2.</li> <li>Ts = (2961xCs) -121] EQ. 2</li> <li>Where Ts = soft-start time in ms, and Cs = BYPASS capacitor in nF.</li> <li>Page 15 - Changed in 1st paragraph, 2nd sentence "(θ<sub>JC</sub> of 5°C/W" to "(θ<sub>JC</sub> of 4.5°C/W"</li> <li>Page 17 - Rotated and changed pad numbers on Metallization Mask layout Updated Die layout X-Y Coordinates table</li> </ol> |

| September 19, 2013 | FN8456.1 | Recommended operating conditions table on page 5, changed VOUT min from 2.5V to 0.6V, and added Note 9. Electrical spec on page 6, Output Noise Voltage, changed test conditions from $I_{LOAD} = 10$ mA, BW = 300Hz < f <300 kHz, BYPASS to GND capacitor = $0.2\mu$ F to $V_{IN} = 4.1$ V, $V_{OU}$ T = 2.5V, $I_{LOAD} = 10$ mA, BW = $100$ Hz < f <100 kHz, BYPASS to GND capacitor = $0.2\mu$ F. Figure 19 on page 11, changed the value from $I_{OUT} = 0.2$ A to $I_{OUT} = 1.5$ A. Figure 20 on page 11, changed the values from $V_{IN} = 4$ V to $V_{IN} = 11$ V and $V_{OUT} = 2.5$ V to $V_{OUT} = 10$ V.                                                |

| May 29, 2013       | FN8456.0 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html